|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Digitaltechnik am eigenen Schreibtisch: Steuerung mit Compact Red Needle |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

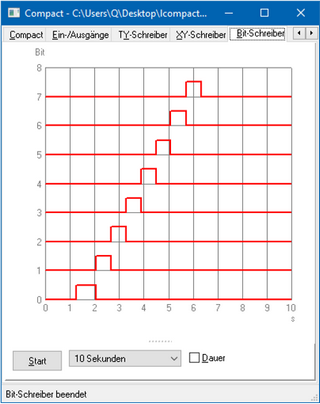

Durch das Hintereinaderschalten mehrerer gleicher IC ist mit diesen drei Steuer-Leitungen eine theoretisch unendliche Anzahl von Ausgängen möglich. Die Funktionsweise eines Schieberegisters kann mit Compact Red Needle manuell und per Programm praktisch analysiert bzw. untersucht werden. Die Abbildung zeigt, dass ein Bit von links nach rechts geschoben wird. Das zu schiebende Bit wird hier über Bit 2 der Digital-Ausgänge gesteuert. Bit 0 entspricht dem Schiebetakt und Bit 1 dem Ausgabetakt. Dies sind die drei Steuerleitungen des Schieberegisters. Die 8 Ausgänge des Schieberegisters sind mit den 8 Eingängen in Compact Red Needle verbunden. Damit kann auch ohne LED auf dem Breadboard die Schiebefunktion verfolgt werden. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

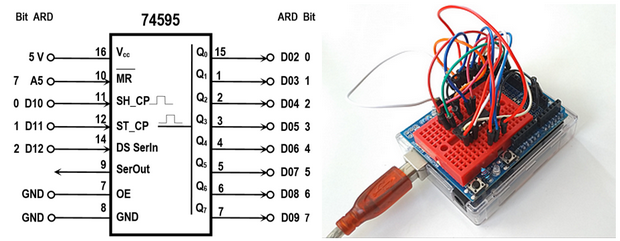

Aufbau mit 15 Verbindungen |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Da 15 Anschlüsse des IC verwendet werden, sind auch entsprechend viele Verbindungen erforderlich, was auf einem kleinen Board schon recht konfus aussehen kann. Die konkrete Verschaltung am Arduino als Compact-Interface ist neben dem Foto schematisch und darunter tabellarisch angegeben.

Als vierte Steuerleitung ist hier das Master-Reset mit Ausgang 7 (A5) verbunden um zu Beginn einer Programmsteuerung eindeutige Verhältnisse zu erhalten.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Steuerung manuell |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

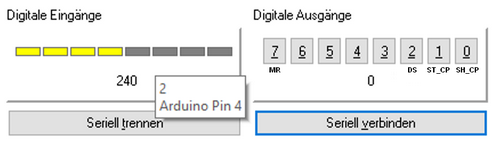

| DOUT 2 legt das zu schiebende Bit fest. Danach übernimmt das Schiebe-Register mit einem Taktwechsel 0-1-0 an DOUT 0 mit dem seriellen Schiebe-Takt den Zustand von DOUT 2. Möchte man das Ergebnis sofort parallel sehen, so muss der Speicher-Takt einmal wechseln, indem DOUT 1 nach 0-1-0 schaltet. Man kann auch erst alle Bits soweit wie gewünscht schieben und erst danach mit DOUT 1 den Zustand des Schieberegisters parallel an den Q-Ausgängen ausgeben.

Angenommen alle digitalen Eingänge in Compact Red Needle sind eingeschaltet. Um die vier rechten Bit gleichzeitig auszuschalten, kann wie folgt verfahren werden:

Damit funktioniert alles wie erwartet und gewünscht. Die Ein-/Ausgänge sollten wie folgt aussehen.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Programm steuert den Bit-Schreiber |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

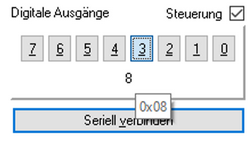

Um den Schiebevorgang wie oben abgebildet im Bit-Schreiber zu verfolgen, ist des nachfolgende Programm erforderlich. Die binäre Schreibweise verdeutlicht die Stellung der digitalen Ausgänge und somit die vier Steuerleitungen in diesem Aufbau.PROGRAMM Ausgänge = OOOOOOIO Ausgänge = IOOOOOOO Schreibe Alle 595-Ausgänge aus, MR aus (an 5 V) Ausgänge = IOOOOIOO Ausgänge = IOOOOIOI Ausgänge = IOOOOOIO Ausgänge = IOOOOOOO Wiederhole Ausgäänge = IOOOOOOI Ausgäänge = IOOOOOIO Bis Durchläufe = 8 ENDE. Dieses Programm als cpf-Datei liegt in Archiv RN74595.zip. Ein Kochrezept zur Durchführung könnte wie folgt aussehen:

Wer lieber mit der Arduino-IDE arbeitet findet in den Arduino-Docs ausführliche Hinweise unter dem Titel Serial to Parallel Shifting-Out with a 74HC595 zu diesem in Arduino-Kreisen weit verbreiteten Baustein. Problem der kompakten RN-Darstellung im Reiter Ein-/Ausgänge: Anklickbare Anzeige ist eine Kombination von Ein- und Ausgabe. Da die Anzeige auch von Programmen gesteuert wird, besteht die Möglichkeit einer Art Rückkopplung, was zu Problemen führen kann, wenn der Reiter Ein-/Ausgänge dargestellt wird. In einer folgenden Version könnte dies durch Ausschalten der Steuerung unterbunden werden. Dadurch ließe sich das in der Zip-Datei ebenfalls vorhandene Lauflicht des Schieberegisters auch fehlerfrei an den gelben LED der Digital-Eingänge beobachten. Dadurch erübrigten sich Vorwiderstände und reale Leuchtdioden.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Theoretischer Hintergrund a closer look |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Die 74er Serie wurde in den 1960er Jahren entwickelt und 1966 als Nachfolger der 54xx-Serie (im Plastik- statt Keramikgehäuse) von Texas Instruments auf den Markt gebracht. Die ältesten Typen existieren seitdem funktional praktisch unverändert. Die Ziffernfolge mit vier bis sechs Stellen wird fortlaufend hochgezählt. Der bekannteste Vertreter ist der 7400, ein 4-fach-NAND-Gatter mit jeweils zwei Eingängen. 74xx – Quelle: Wikipedia

HC steht dabei für eine Variante in High-Speed-CMOS-Technologie. Das Schieberegister besteht im Kern aus 8 D-Flip-Flops, auch Register oder Bit-Speicher genannt. Ein solches Flip-Flop hat einen D-Eingang und einen Q-Ausgang. Der Ausgang Q folgt dem Eingang D. Ist eine Taktsteuerung vorhanden, so folgt der Ausgang Q erst dann dem Eingang D, wenn der Takt aktiv wird. Durch die Hintereinanderschaltung wandert der Zustand am ersten FF, dem seriellen Eingang, in Form einer 1 oder 0 nacheinander durch. Um diese Zustände gleichzeitig an parallele Anschlüsse zu leiten, sind diese Schiebe-FF mit jeweils einem weiteren D-FF verbunden. Erst wenn der Takt dieser Ausgabe-Register reagiert, werden die Inhalte der Schiebe-FF zeitgleich, also synchron an den Ausgang weitergegeben. Datenblätter zeigen entsprechende Prinzipschaltbilder. Vom D-Flip-Flop zum NOR-Gatter Ein D-FF ist ein JK-MS-FF mit einem Inverter zwischen J und K. Der J-Eingang ist dann identisch mit D und dieser schaltet den Ausgang Q an oder aus, je nach dem Signal an D. Ein JK-MS-FF besteht aus zwei JK-FF, wobei das erste JK-FF auf die ansteigende und das zweite JK-FF auf die abfallende Flanke des parallel zugeführten Taktes reagiert, oder jeweils umgekehrt. Ein JK-FF ist ein RS-FF dessen Ausgänge über ein Zweier-UND mit dem jeweils anderen Eingang verbunden sind. Der unerwünschte Zustand R=S=1 entfällt dadurch und wird ersetzt durch J=K=1, was dazu führt, dass der Speicherzustand bzw. Ausgang Q bei jedem Taktwechsel kippt. Dies führt auch zu einer Takthalbierung, was der Konstruktion einfacher Asynchron-Zähler dienen kann. Taktgesteuerte RS-FF entstehen durch Vorschaltung von zwei 2er-NANDs, wobei jeweils ein Eingang des jeweiligen UND mit dem Taktsignal verbunden ist. Soll nur auf die abfallende oder aufsteigende Flanke reagiert werden, kommt eine weitere Modifikation des Takteinganges hinzu, so dass sogenannte Taktflanken-gesteuerte Kippstufen oder Flip-Flops entstehen. Ein RS-FF entsteht aus zwei NAND- oder zwei NOR-Gattern. Somit schließt sich der Kreis im Kapitel 6 zur Digitaltechnik, wo ein Set-Reset-Flip-Flop aus zwei NOR als Programm bereits dargestellt ist.

|

Compact Red Needle

MSR mit Arduino & Compact

Mehr Software

| Startseite | Bücher | Software | Digital RTV | Musik | Kontakt |

Für Inhalt und weitere Verzweigung externer Links sind die Betreiber der dortigen Seiten verantwortlich - H.-J. Berndt